Contenu

Jeu d'instructions

Ce processeur, inspiré des microprocesseurs ARM Cortex, dispose d'un banc de 8 registres de 16 bits. Pour simplifier sa conception, il dispose d'un registre à part pour le compteur ordinal. Son architecture est de type RISC (Reduced Instruction Set), load/store (seules les instructions de chargement et d'écriture de registre accèdent à la mémoire), et dispose d'instructions arithmétiques à 3 adresses (un registre pour le résultat, un registre pour chacun des opérandes).

Pour simplifier sa conception, les instructions tiennent sur un mot de 16 bits lorsqu'elle utilisent l'adressage par registre, et sur 2 mots de 16 bits lorsqu'elles utilisent l'adressage immédiat (opérations arithmétiques) ou direct (branchement), la valeur de l'opérande étant stockée dans le mot qui suit le code de l'instruction. Dernière entorse aux principes des RISC, ce processeur dispose d'un registre d'état qui mémorise le résultat des comparaisons.

Le jeu d'instructions est le suivant :

| Mnémonique | Description |

|---|---|

| ldr rx,[ry] | charge le registre rx avec le contenu de la mémoire à l'adresse contenue dans ry |

| ldr rx,adresse | charge le registre rx avec le contenu de la mémoire à l'adresse adresse |

| str rz,[ry] | écrit le contenu du registre rz en mémoire à l'adresse contenue dans ry |

| str rz,adresse | écrit le contenu du registre rz en mémoire à l'adresse adresse |

| mov rx,ry | charge la valeur du registre ry dans le registre rx |

| mov rx,#val | charge la valeur immédiate val dans le registre rx |

| add rx,ry,rz | charge le registre rx avec la somme des registres ry et rz |

| add rx,ry,#val | charge le registre rx avec la somme du registre ry et de val |

| sub rx,ry,rz | charge le registre rx avec la différence des registres ry et rz |

| sub rx,ry,#val | charge le registre rx avec la différence du registre ry et de val |

| cmp ry,rz | change les indicateurs N et Z du registre d'état en fonction de la différence ry-rz |

| cmp ry,#val | change les indicateurs N et Z du registre d'état en fonction de la différence ry-val |

| beq rz | saute à l'adresse contenue dans rz si le bit Z du registre d'état vaut 1 |

| beq address | saute à l'adresse address si le bit Z du registre d'état vaut 1 |

| blt rz | saute à l'adresse contenue dans rz si le bit N du registre d'état vaut 1 |

| blt address | saute à l'adresse address si le bit N du registre d'état vaut 1 |

| b rz | saute à l'adresse contenue dans rz |

| b address | saute à l'adresse address |

Programmes de test

Un assembleur est disponible pour traduire les mnémoniques en code machine. Cet assembleur permet de définir des étiquettes afin de faciliter l'écriture des branchements.

Cet assembleur est très rustique et ne donne pas de message très explicite en cas d'erreur. Quand il parvient à assembler le fichier source, il produit un fichier .lst qui reprend le code source en face du code généré, et un fichier .mem à charger dans le composant mémoire de Logisim.

Voici un petit programme de test pour vérifier le fonctionnement du processeur :

L'assembleur reconnaît les pseudo-instructions smw qui permet de réserver un mot mémoire en lui donnant une valeur, et rmw qui réserve un certain nombre de mots mémoire :

L'assembleur reconnaît également les noms symboliques sp (Stack Pointer) pour r6 et lr (Link Register) pour r7. Il accepte aussi les instructions push et pop qu'il émule en générant le code pour empiler la valeur d'un registre ou dépiler une valeur dans un registre.

Format des instructions

| instruction | code | imm | rx | ry | rz | |||

|---|---|---|---|---|---|---|---|---|

| 4 bits | 1 bit | 3 bits | 3 bits | 3 bits | 2 bits | |||

| ldr rx,[ry] | 0000 | 0 | rx | ry | ||||

| ldr rx,adresse | 0000 | 1 | rx | |||||

| adresse | ||||||||

| str rz,[ry] | 0001 | 0 | ry | rz | ||||

| str rz,adresse | 0001 | 1 | rz | |||||

| adresse | ||||||||

| mov rx,ry | 0010 | 0 | rx | ry | ||||

| mov rx,#val | 0010 | 1 | rx | |||||

| val | ||||||||

| add rx,ry,rz | 0011 | 0 | rx | ry | rz | |||

| add rx,ry,#val | 0011 | 1 | rx | ry | ||||

| val | ||||||||

| sub rx,ry,rz | 0100 | 0 | rx | ry | rz | |||

| sub rx,ry,#val | 0100 | 1 | rx | ry | ||||

| val | ||||||||

| cmp ry,rz | 0101 | 0 | ry | rz | ||||

| cmp ry,#val | 0101 | 1 | ry | |||||

| val | ||||||||

| beq rz | 0110 | 0 | rz | |||||

| beq adresse | 0110 | 1 | ||||||

| adresse | ||||||||

| blt rz | 0111 | 0 | rz | |||||

| blt adresse | 0111 | 1 | ||||||

| adresse | ||||||||

| b rz | 1000 | 0 | rz | |||||

| b adresse | 1000 | 1 | ||||||

| adresse | ||||||||

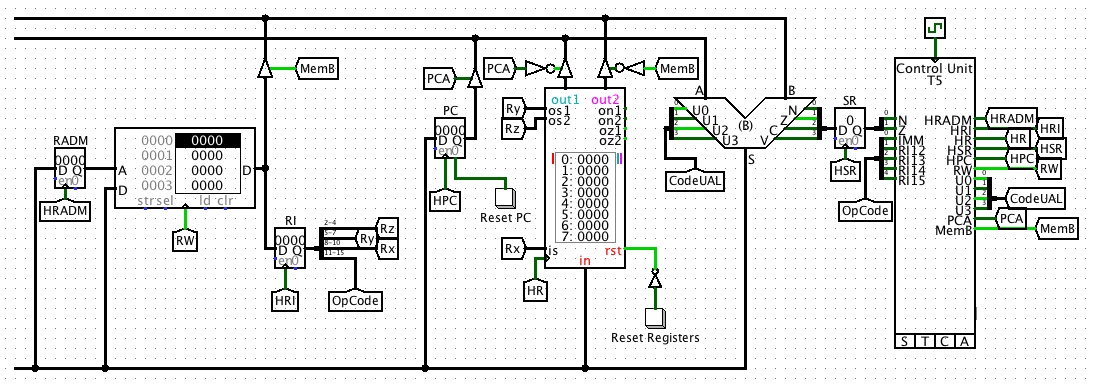

Chemin de données

Logisim

Vous trouverez ci-dessous les versions de Logisim pour :

- Mac OS

- Logisim-mac-Java.zip, décompressez l'archive et placez l'application Logisim où vous voulez, par exemple dans le dossier Applications de votre Mac.

- Linux

- logisim-linux.tgz, décompressez l'archive, placez le dossier Logisim là où vous le souhaitez, puis, dans un terminal, placez vous dans ce dossier et exécutez la commande

./install.sh. Il suffit ensuite de double-cliquer sur le fichier Logisim pour lancer l'application. - Windows

- logisim-windows.exe