Les portes logiques et les opérateurs arithmétiques que nous avons construits calculent des fonctions de leurs entrées. Ils n'ont pas de mémoire et ne stockent pas d'information. On dit que ce sont des circuits combinatoires car leurs sorties sont obtenues en combinant la valeur de leurs entrées.

Nous allons maintenant construire des circuits qui mémorisent de l'information. Ces circuits ont un état permanent, et leurs sorties dépendent de leurs entrées et de cet état.

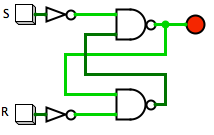

La bascule RS

Afin de mémoriser une valeur dans un circuit, on reboucle une sortie de ce circuit sur une de ses entrées. Ainsi, le circuit auto-alimente une de ses entrées et peut conserver un état permanent. Les autres entrées sont utilisées pour changer cet état. L'exemple le plus simple d'un tel circuit est la bascule RS (Reset/Set) qui permet de mémoriser un bit. On met se bit à 1 avec l'entrée Set, et on le met à zéro avec l'entrée Reset.

Dans le circuit ci-dessus, la sortie peut initialement prendre une valeur quelconque. En effet, lorsque les boutons R et S ne sont pas enfoncés, les entrées correspondantes des portes NAND sont à 1. Si la sortie vaut 1, l'entrée supérieure de la porte du bas est à 1, donc sa sortie est à 0, et l'entrée inférieure de la porte du haut est donc à 0, la sortie vaut donc 1. On a bien un état stable. Si la sortie vaut 0, l'entrée supérieure de la porte du bas vaut 0, donc sa sortie vaut 1, ainsi que l'entrée inférieure de la porte du haut. La sortie vaut donc 0, et on a un autre état stable.

Si on appuie sur le bouton S, sa sortie passe à 1, et l'entrée supérieure de la porte du haut passe à 0. Sa sortie passe donc à 1, et le circuit bascule dans l'état stable où sa sortie vaut 1. Cet état est conservé même lorsqu'on relâche le bouton S car la porte du bas maintient l'entrée inférieure de la porte du haut à 0.

Si on appuie sur le bouton R, sa sortie passe à 1, et l'entrée inférieure de la porte du bas passe à 0. Sa sortie passe donc à 1, et la sortie de la porte supérieure passe à 0. Le circuit bascule dans l'état stable où sa sortie vaut 0. Cet état est conservé lorsqu'on relâche le bouton R car la porte du haut maintien l'entrée supérieure de la porte du bas à 0.

Ce circuit mémorise donc le dernier bouton sur lequel on a appuyé : sa sortie vaut 1 s'il s'agit du bouton S, elle vaut 0 s'il s'agit du bouton R.

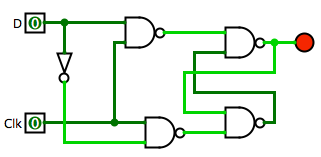

Bascule D simple

On peut utiliser une bascule RS pour mémoriser un bit sur commande d'un signal que l'on appelle généralement une horloge, notée Clk (abréviation de l'anglais clock). On appelle la donnée à mémoriser D (pour data). Il suffit pour cela de construire les entrées R et S de la bascule RS à partie de D et de Clk, de façon à ce que la sortie prenne la valeur de D quand Clk vaut 1, et ne change pas quand Clk vaut 0. On obtient alors une bascule D :

Les deux portes de droite constituent une bascule RS dont les entrées sont calculées par les trois portes de gauche à partir de D et Clk. On a {$S=Clk\wedge D$} et {$R=Clk\wedge \overline{D}$}. Ainsi, la bascule RS ne change d'état que si Clk vaut 1, et elle passe un 1 si D vaut 1, et à 0 si D vaut 0. On a donc bien un circuit qui enregistre la valeur de D quand Clk vaut 1, et qui la conserve quand Clk vaut 0.

Un tel circuit, qui peut changer d'état à n'importe quel moment (ici, quand Clk vaut 1, la sortie suit la valeur de l'entrée D), est dit asynchrone. Il est souvent beaucoup plus facile de concevoir des circuits complexes quand on maîtrise l'instant auquel ont lieu les changement d'état. Nous allons pour cela construire une autre version de la bascule D, qui mémorise la valeur de D au moment précis ou son horloge Clk passe de 0 à 1.

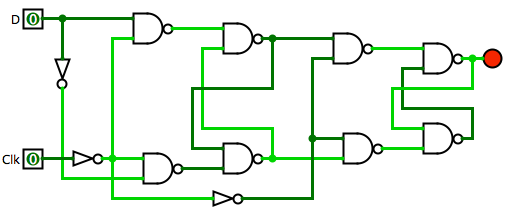

Bascule D maître-esclave

Pour construire une bascule D qui fonctionne de manière synchrone, c'est-à-dire qui ne change d'état que sur les fronts montants de son horloge Clk, le principe est de mettre en cascade deux bascules D asynchrones dont les horloges sont en opposition de phase. La première bascule, dite maître, a pour horloge l'inverse de Clk. Sa sortie suit donc la valeur de D quand l'horloge Clk est à 0. La seconde bascule, dite esclave, a pour horloge Clk. Sa sortie suit la valeur de la sortie de la bascule maître quand Clk vaut 1. Ainsi, quand Clk vaut 0, la bascule maître suit la valeur de D, et la bascule esclave est figée. Quand Clk vaut 1, la bascule maître est figée, et la bascule esclave suit sa sortie. La sortie de la bascule maître-esclave ne change donc que lorsque Clk passe de 0 à 1.

Pour que cela fonctionne, il faut que la bascule maître se mette à suivre la valeur de D juste avant que la bascule esclave se fige. De même, lorsque Clk repasse à 0, pour que la sortie ne change pas, il faut que l'entrée D reste stable le temps que la bascule maître se fige.

Le changement d'état d'une telle bascule ne se fait donc pas exactement sur un front montant de Clk, mais la durée pendant laquelle le maître et l'esclave sont tous les deux en mode suiveur est suffisamment courte pour que l'on puisse considérer qu'il s'agit d'une bascule synchrone.

Les circuits présentés sur cette page sont disponibles pour Logisim.